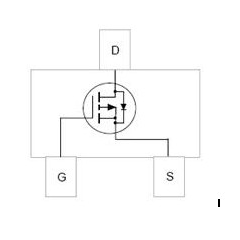

D-FET je u pristranosti 0 vrata kada postojanje kanala može voditi FET; E-FET je u prednaponu 0 vrata kada nema kanala, ne može provoditi FET. ove dvije vrste FET-ova imaju svoje karakteristike i namjene. Općenito, poboljšani FET u brzim krugovima male snage vrlo je vrijedan; i ovaj uređaj radi, to je polaritet pristranosti vrata voltage i odvod napon istog, prikladniji je u dizajnu strujnog kruga.

Takozvano pojačano znači: kada je VGS = 0 cijev granično stanje, plus ispravan VGS, većina nositelja privučena je vratima, čime se "poboljšavaju" nosioci u regiji, tvoreći vodljivi kanal. n-kanalni poboljšani MOSFET je u osnovi lijevo-desna simetrična topologija, koja je P-tip poluvodiča na stvaranju sloja izolacije SiO2 filma. On stvara izolacijski sloj SiO2 filma na poluvodiču P-tipa, a zatim difuzira dva visoko dopirana N-tipa područja pomoćufotolitografija, i vodi elektrode iz područja N-tipa, jednu za odvod D i jednu za sors S. Sloj metalnog aluminija postavljen je na izolacijski sloj između izvora i odvoda kao vrata G. Kada je VGS = 0 V , postoji dosta dioda s diodama uzastopno postavljenim između odvoda i izvora, a napon između D i S ne tvori struju između D i S. Struja između D i S ne nastaje pomoću primijenjeni napon.

Kada se doda napon gejta, ako je 0 < VGS < VGS(th), kroz kapacitivno električno polje formirano između gejta i supstrata, polionske rupe u poluvodiču P-tipa blizu dna gejta se odbijaju prema dolje, i pojavljuje se tanki osiromašeni sloj negativnih iona; u isto vrijeme, privući će oligone koji se nalaze u njemu da se pomaknu na površinski sloj, ali broj je ograničen i nedovoljan za formiranje vodljivog kanala koji povezuje odvod i izvor, tako da je još uvijek nedovoljan za formiranje ID struje odvoda. daljnje povećanje VGS, kad VGS > VGS (th) (VGS (th) se naziva napon uključivanja), jer je u to vrijeme napon vrata bio relativno jak, u površinskom sloju poluvodiča P-tipa blizu dna vrata ispod skupljanja više elektrona, možete formirati jarak, odvod i izvor komunikacije. Ako se u ovom trenutku doda napon izvora odvoda, struja odvoda može se formirati ID. elektroni u vodljivom kanalu formiranom ispod vrata, zbog rupe nosača s P-tipom poluvodiča polaritet je suprotan, pa se naziva anti-tip sloj. Kako VGS nastavlja rasti, ID će se nastaviti povećavati. ID = 0 pri VGS = 0 V, a odvodna struja javlja se tek nakon što je VGS > VGS(th), pa se ova vrsta MOSFET-a naziva poboljšani MOSFET.

Regulacijski odnos VGS na struju odvoda može se opisati krivuljom iD = f(VGS(th))|VDS=const, koja se naziva krivulja prijenosne karakteristike, a veličina nagiba krivulje prijenosne karakteristike, gm, odražava kontrolu struje odvoda pomoću napona izvora vrata. veličina gm je mA/V, pa se gm također naziva transkonduktivnost.